Distribution-demandcreation upturn Pg 52

JUNE

Issue 11/2009 www.edn.com A modest proposal for IP Pg 7

Endpoint distortion Pg 14

Design Ideas Pg 41

Product Roundup Pg 54

Tales from the Cube Pg 58

# VOICE OF THE ENGINEER

# TEEUPYOUR MULTIPROCESSING OPTIONS Page 24

USE 3.0: A SIMPLE IDEA FULL OF CHALLENGES

Page 16

# RF ENGINEERS AUTOMATE TESTS

Page 20

TROUBLESHOOTING A TRANSACTION-LEVEL MODEL

Page 31

DESIGNING PORTABILITY INTO SILICON IP

Page 37

**64-PIN OFP, PACKAGE STYLE HO JEDEC MO-188**

(actual footprint)

**ASIA PACIFIC**

+852 2376-0801 JAPAN

+81 (3) 5226-7757

LEARN MORE AT

www.cirrus.com/sa303edn

EUROPE/UK +44 (0) 1628-891-300

# **3 A, Three-Phase Motor Driver IC Uses Protection Features to Deliver Performance Gains**

The SA303-IHZ is a pulse width modulation (PWM) motor driver IC designed to protect brushless motors from operational hazards such as over current, under voltage and over temperature. This newest addition to the Apex Precision Power™ product family can generate performance gains in the overall motor control circuitry by eliminating motor shutdown and re-starts. For example, should an over-temperature or short circuit occur, the SA303-IHZ will not shutdown the outputs but instead allows the system to continue running while it signals the external controller to take corrective action. In most cases, the processor can correct the condition by utilizing software to remedy the external interrupt.

### **APPLICATIONS**

- Motor Drives Industrial Controls

- Factory Automation

- Robotics

- Motor Drives Office Equipment

- Copiers, Fax Machines

- Vending Machines

- Motor Drives Aerospace, Military

- Positioning Control

- Aircraft Seating

Production Supply Voltage Motor Output Model Volume Pricing Interface Current Operation 10K Pieces USD\* Brushless 3 A continuous 10 V to 60 V SA303-IHZ \$5.86 DC Motor 10 A Peak Single Supply Brushless < 9 V to 60 V 5 A continuous SA306-IH7 \$9.90 17 A PEAK DC Motor Single Supply Brushless 8 A continuous < 9 V to 60 V SA306A-FHZ \$12.85 DC Motor 17 A PEAK Single Supply 10 V to 60 V Brush 3 A continuous SA53-IHZ \$4 79 DC Motor 10 A Peak Single Supply 5 A continuous < 9 V to 60 V Brush SA57-IH7 \$7.15 DC Motor 17 A PEAK Single Supply Brush 8 A continuous < 9 V to 60 V SA57A-FH7 \$9.05 DC Motor 17 A PEAK Single Supply

ber unit pricing for production estimating only: actual per unit cost through distribution may vary

**REQUEST A FREE SAMPLE!** Request a free sample unit of the SA303-IHZ By visiting www.cirrus.com/sa303edn

For product selection assistance or technical support with Apex Precision Power™ products call 1-800-546-2739 or apex.support@cirrus.com.

# © 2009 Cirrus Logic, Inc. All rights reserved. Cirrus Logic, Cirrus Logic, Logic Logic, Logic, Logic, Anex Precision, Power, Anex and the Anex Precision Power Logic

designs are trademarks of Cirrus Logic, Inc. All other brands and product names may be trademarks or service marks of their respective owners. EDN6112009

nntke

Diniske

An additional 1,000,000+ components can be sourced at digikey.com

The industry's broadest product selection available for immediate delivery

**NRPNRATIN**

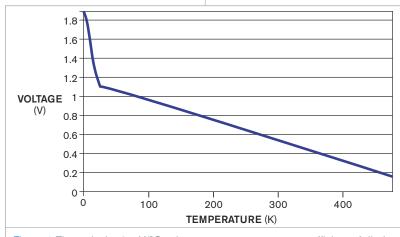

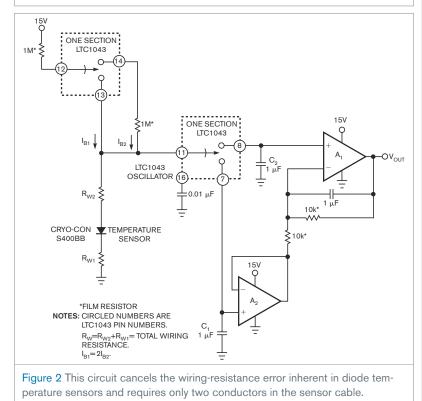

NH- 9284

# www.digikey.com 1.800.344.4539

\*Digi-Key is an authorized distributor for all supplier partners. New products added daily. © 2009 Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

# "How can I tell if a power supply is reliable?"

# There's an indicator on the front.

It says "Agilent." With a typical MTBF of 40,000 hours, over half-acentury of experience, and with more than 250 models to choose from, Agilent's power supplies are the ones you can count on. In fact the array of our power supplies is so extensive, it wouldn't fit on this page. For clean, low-noise, programmable power to countless DUTs, there's an Agilent power supply with your name on it. Actually, it's our name on it, but you know what we mean.

> Take a brief quiz and save up to 10%. And enter to win an iPod touch. www.agilent.com/find/poweronquiz

> > Agilent Authorized Distributor

866-436-0887 www.metrictest.com/agilent

© Agilent Technologies, Inc. 2009. Limited time offer. See Web site for full promotion details. Discount offer applies to 144 power supplies.

# **Agilent Technologies**

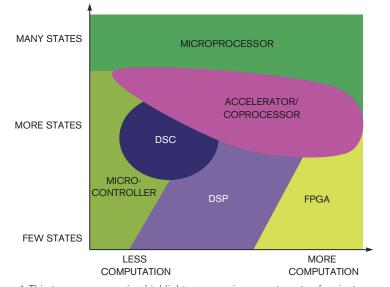

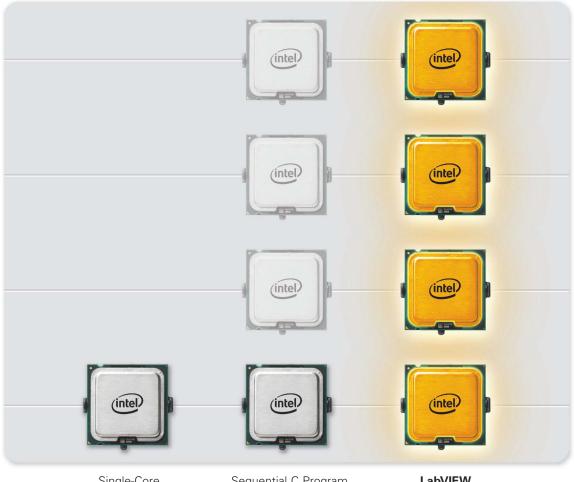

# Tee up your multiprocessing options

A good processor taxonomy helps you understand processing architectures' sweet spots. You should probably look at multicore options in the same way.

by Robert Cravotta, Technical Editor

- Low-power audio codec incorporates Class D-loudspeaker pri amplifier

- 8 Two-terminal current source supplies 200 mA

8

- Agilent, ETS-Lindgren address A-GPS test

- 10 Kits support design of fieldoriented-control motor drives

- 10 Standardization boosts software reuse in microcontrollers

- 11 Op amp has offset calibration to 200  $\mu V$

11 CES 2009: the price of falling prices

USB 3.0: a simple

idea full of challenges

Combining 5 Gbps with

by Ron Wilson, Executive Editor

O the convenience of USB

sounds like a sure win. but many

issues are hiding behind the

premise.

EDN 6.11.09 contents

- 12 Texas Instruments announces dual 14-bit, 250M-sample/sec ADC

- 12 Passive scope probes offer bandwidths to 1.5 GHz for high-speed-digital applications

- 13 Research Update: New "nonblinking" nanocrystals promise increased efficiency in LED lighting; IMEC develops design for deep-brain stimulation implant

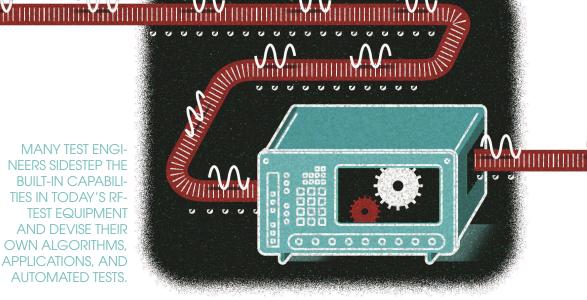

# RF engineers automate tests

20 Many test engineers sidestep the built-in capabilities in today's RF-test equipment and devise their own algorithms, applications, and automated tests.

*by Martin Rowe, Senior Technical Editor,* Test & Measurement World

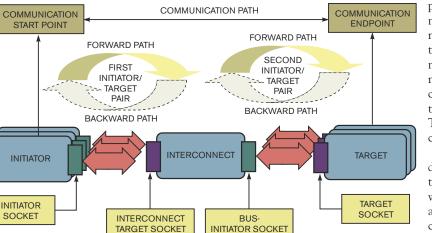

# Troubleshooting a transaction-level model

31 Seemingly minor violations of the TLM 2.0 standard can turn a system-level model into an agent of evil in your design flow.

> by Andrea Kroll, PhD, Jeda Technologies

# Designing portability into silicon IP

37 Design foundry portability into IP cores, rather than applying it after the fact. by Joseph Pun, Gennum Corp, Snowbush IP Group

# DESIGNIDEAS

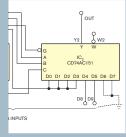

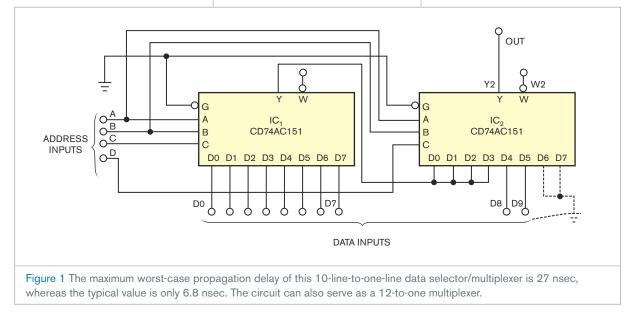

41 Fast 10-line-to-one-line data selector/multiplexer comprises only two ICs

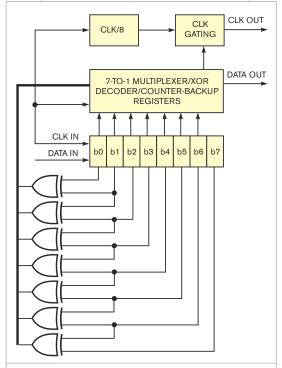

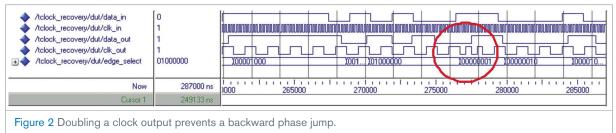

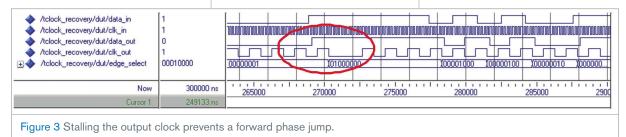

42 Implement a simple digital-serial NRZ data-recovery algorithm in an FPGA

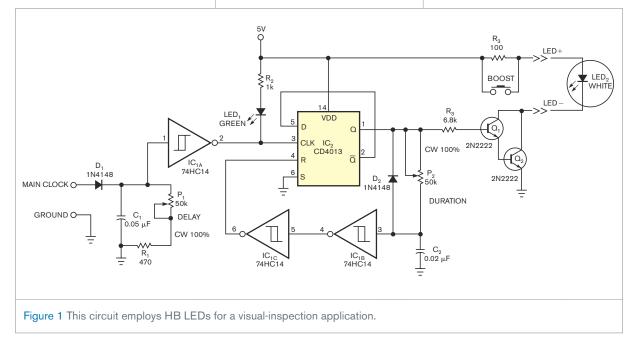

44 LED strobe has independent delay and duration

48 Cancel sensor-wiring error with bias-current modulation

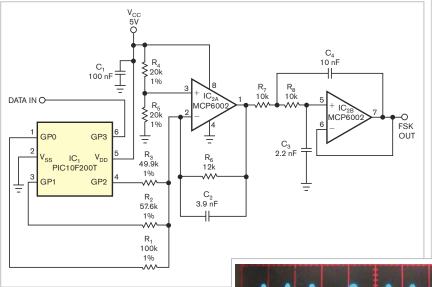

50 Simple FSK modulator enables data transmission over low-speed link

$2\mu W$  nanoPower

Actel IGLOO<sup>®</sup> nano and ProASIC<sup>®</sup>3 nano low-power FPGAs bring reprogrammability to high-volume applications at the lowest cost. Available in 3x3 mm packages, with prices starting at only 49¢ (and 50 variants under \$1.00), Actel gives you the industry's widest selection of low-power, low- cost FPGAs. With power consumption as low as 2  $\mu$ W, IGLOO nano and ProASIC3 nano FPGAs are perfect for your volume-driven, power-sensitive applications. Now, more than ever, power matters.

Watch webcasts, read white papers, and get a starter kit at actel.com/nanoFPGAs

volt ski tolati

# contents 6.11.09

# **DEPARTMENTS & COLUMNS**

- 7 EDN.comment: A modest proposal for IP

- 14 Signal Integrity: Endpoint distortion

- 52 **Supply Chain:** Economy opens more doors to demand creation for distributors; System ICs set for double-digit growth in 2010; EPA finding on gases could affect US IC manufacturing

- 54 **Product Roundup:** Power Sources, ICs, Computers and Peripherals, Embedded Systems

- 58 Tales from the Cube: The boss is always right, even when he's wrong

# **EDN**) online contents

# www.edn.com

# ONLINE ONLY

Check out these Web-exclusive articles:

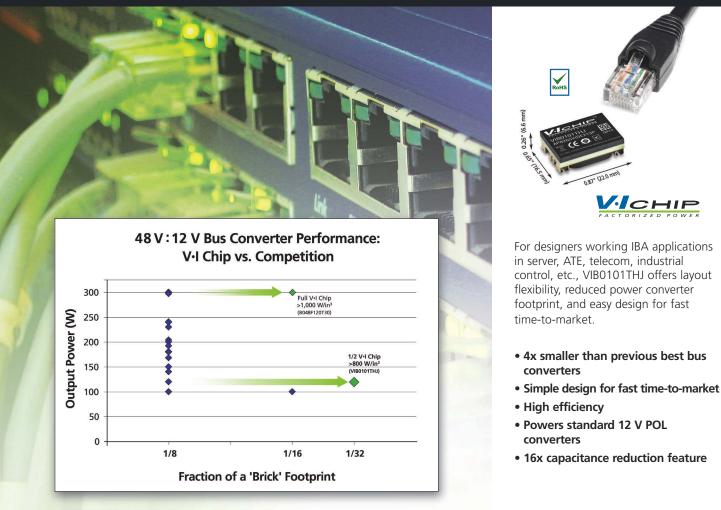

# For 10-Gbps interconnects, the RJ-45 once again will dominate

The industry will adopt 10-GBase-T as the primary 10-Gbps interconnect for data-center switches and servers for many of the same reasons that RJ-45 and twisted-pair cabling dominate at gigabit speeds. →www.edn.com/article/CA6656523

# Electronic-ballast circuits enhance resonant-mode power supplies

This article explains the basic functions of a typical electronic-ballast circuit, highlights the similarities between the applications, and describes a typical resonant-mode power supply using a standard electronic-ballast-control IC. →www.edn.com/article/CA6658506

# SEE NAKED ICs

The IC Insider, an exclusive EDN.com series contributed by Chipworks, one of the leading IC reverse-engineering

houses, provides detailed functional and circuit analysis of significant new ICs. The IC Insider shows you how the latest ICs really work, and why–insight you'll never get from the data sheet.

# **HOT TOPICS**

Check out *EDN*'s Hot Topics pages. Hot Topics pages deliver continuously updated, subject-specific links from not only *EDN* but also the entire electronics-industry Web. →www.edn.com/hottopics

EDN ® (ISSN#0012-7515), (GST#123397457) is published biweekly, 24 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. Tad Smith, Chief Executive Officer; Mark Finkelstein, President, Boston Division. Periodicals postage paid at Littleton, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN ®, PO Box 7500, Highlands Ranch, CO 80163-7500. EDN % of St. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN ®, PO Box 7500, Highlands Ranch, CO 80163-7500. EDN % of St. GST# 123397457); Mexico, \$229.990 one year, air expedited, \$399.99 one year. (Sanda, \$22999 one year (Includes 7% GST, GST# 123397457); Mexico, \$229.990 one year, air expedited, \$399.99 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Agreement No. 40685520. Return undeliverable Canadian addresses to: RCS International, Box 697 STN A, Windsor Ontario N3A 6N4. E-mail: Subsmail@ReedBusiness.com. Please address all subscription mail to EDN ®, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN ® is a registered trademark of Reed Elsevier Properties Inc, used under license. A Reed Business Information, Publication/Volume 54, Number 11 (Pinited in USA).

- 0.4 Watts to 150 Watts

Power Transformers

- 115V/26V-400/800 Hz Primary

- Secondary Voltages 2.5V to 300V

- Manufactured to MIL-PRF 27 Grade 5, Class S, (Class V, 155°C available)

- Surface Mount or Plug-In

- Smallest possible size

See Pico's full Catalog immediately www.picoelectronics.com

# PICO Electronics, Inc

143 Sparks Ave., Pelham, NY 10803 Call Toll Free: 800-431-1064 E Mail: info@picoelectronics.com FAX: 914-738-8225

Delivery - Stock to one week INDUSTRIAL • COTS • MILITARY

### PRESIDENT, BOSTON DIVISION, REED BUSINESS INFORMATION Mark Finkelstein, mark.finkelstein@reedbusiness.com; 1-781-734-8431

PUBLISHER, EDN WORLDWIDE Russell E Pratt 1-781-734-8417; rpratt@reedbusiness.com

### ASSOCIATE PUBLISHER. EDN WORLDWIDE

Judy Hayes 1-925-736-7617; judy.hayes@reedbusiness.com

### VICE PRESIDENT, EDITORIAL DIRECTOR

Karen Field 1-781-734-8188; kfield@reedbusiness.com

EDITOR-IN-CHIEF. EDN WORLDWIDE Rick Nelson 1-781-734-8418

> rnelson@reedbusiness.com EXECUTIVE EDITOR

Ron Wilson 1-510-744-1263; ronald.wilson@reedbusiness.com

# MANAGING EDITOR

Amv Norcross 1-781-734-8436; fax: 1-720-356-9161; amy.norcross@reedbusiness.com

Contact for contributed technical articles SENIOR ART DIRECTOR

Mike O'Leary 1-781-734-8307; fax: 1-303-265-3021; moleary@reedbusiness.com

ANALOG Paul Rako Technical Editor 1-408-745-1994; paul.rako@edn.com

MASS STORAGE, MULTIMEDIA, PCs. AND PERIPHERALS

Brian Dipert Senior Technical Editor 1-916-760-0159; fax: 1-303-265-3187; bdipert@edn.com

MICROPROCESSORS, DSPs, AND TOOLS Robert Cravotta Technical Editor 1-661-296-5096; fax: 1-303-265-3116; rcravotta@edn.com

### NEWS Suzanne Deffree Managing Editor 1-631-266-3433; sdeffree@reedbusiness.com

POWER SOURCES, ONLINE INITIATIVES Maraery Conner Technical Editor 1-805-461-8242; fax: 1-805-461-9640; mconner@reedbusiness.com

**DESIGN IDEAS EDITOR** Martin Rowe Senior Technical Editor, Test & Measurement World edndesignideas@reedbusiness.com SENIOR ASSOCIATE EDITOR

Frances T Granville 1-781-734-8439; fax: 1-303-265-3131; f.granville@reedbusiness.com EDITORIAL/WEB PRODUCTION

Diane Malone

Manager 1-781-734-8445; fax: 1-303-265-3024 Steve Mahoney Production/Editorial Coordinator 1-781-734-8442 fax: 1-303-265-3198 Melissa Annand Newsletter/Editorial Coordinator

1-781-734-8443; fax: 1-303-265-3279 Adam Odoardi Prepress Manager 1-781-734-8325; fax: 1-303-265-3042

CONSULTING EDITOR Jim Williams, Staff Scientist, Linear Technology

# CONTRIBUTING TECHNICAL EDITORS

Dan Strassberg strassbergedn@att.net Nicholas Cravotta editor@nicholascravotta.com

COLUMNISTS Howard Johnson, PhD, Signal Consulting Bonnie Baker, Texas Instruments Pallab Chatterjee, SiliconMap

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000. Address changes or subscription inquiries: phone 1-800-446-6551; fax 1-303-470-4280; subsmail@reedbusiness.com. For a free subscription, go to www.getfreemag.com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

PRODUCTION

Dorothy Buchholz Group Production Director 1-781-734-8329 Joshua S Levin-Epstein Production Manager 1-781-734-8333; fax: 1-781-734-8096

### EDN EUROPE

Graham Prophet, Editor, Reed Publishing The Quadrant, Sutton, Surrey SM2 5AS +44 118 935 1650; fax: +44 118 935 1670; gprophet@reedbusiness.com

EDN ASIA

Luke Rattigan, Chief Executive Officer luke.rattigan@rbi-asia.com Kirtimava Varma, Editor-in-Chief kirti.varma@rbi-asia.com

### EDN CHINA

William Zhang, Publisher and Editorial Director wmzhang@idg-rbi.com.cn Jeff Lu, Executive Editor iefflu@rbichina.com.cn

### EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Ken Amemoto, Editor-in-Chief amemoto@reedbusiness.jp

# 2 KW TO 900 KW+ AC/DC POWER SUPPLIES

|               | (1 III     |               |              |                |

|---------------|------------|---------------|--------------|----------------|

| Specification | XR Series  | TS Series III | MS Series II | MT Series III  |

| Models        | 54         | 150           | 84           | 140            |

| Power         | 2 to 6 kW  | 5 to 45 kW    | 30 to 75 kW  | 100 to 900 kW+ |

| Voltage       | 0-1000 Vdc | 0-4000 Vdc    | 0-4000 Vdc   | 0-4000 Vdc     |

| Current       | 0-375 Adc  | 0-2700 Adc    | 0-4500 Adc   | 0-24000 Adc    |

|               |            |               |              |                |

AGNA-POWER

**ECTRONICS**

# Applications

- Electric Powertrains

- Water Treatment

- Military Battery Charging

- Aviation Systems

- Source Emulation

- Laboratory Testing

- PLC Integration

- Many more

Announcing the <u>XR Series</u>: The Highest Power Density 2U Programmable DC Power Supply

- 📀 Voltages up to 1000 Vdc, Currents up to 375 Adc

- 🔇 Current-fed processing S-232 standard, LXI Ethernet, GPIB, USB, RS485 available

www.magna-power.com • (908) 237-2200

MT Series IV

EDN.COMMENT

# BY RON WILSON, EXECUTIVE EDITOR

# A modest proposal for IP

he US patent system needs fixing to the point that there are debates over just whose interests we should fix first. But no one seems any longer interested in the original idea: that patents protect the inventor—not a corporation—and that, by protecting the inventor, they encourage publication, accelerating the pace of innovation. So here's a suggestion: We should prohibit the assignment, the sale, or any other transfer of patent ownership, except for inheritance.

This change would not fix everything. But it would resolve a number of problems that corrode the system, and correct one problem that threatens to blow up the whole show.

First, consider the inventors. Today, granting patents to the people who did the inventing is fiction. Unless the inventor is self-employed and not under contract, an employer gets the patent. This appropriation is poisonous in a number of ways.

Engineers find ways to work around the system. They avoid documentation. If an idea starts to pan out, the engineer quits, launches a new company, and then files patents. That move is risky, but it is a better deal than getting your name on a bronze plaque in somebody else's lobby. Most of the time, the industry and the company that funded the work get nothing, and the inventor gets two years of 16-hour days at reduced salary. And that scenario is what happens if everyone avoids litigation.

Now consider employers. The system vacuums the best R&D employees from organizations just as they are about to do their most valuable work. Any way you look at it, that move Let inventors own their patents and allow them to transfer limited rights under the well-developed body of licensing law.

destroys equity. Further, owning patents tends to force companies to focus on generating revenue from their patents—and away from serving their customers.

Suppose patents were not transferable, however. Inventors, instead of assigning patents to their employers, would license them in case-by-case negotiations based on the employment agreement. With licensing instead of assignment, the goals of the inventor and employer would align: Both want to maximize the profits from the patent, and the best way to do that is usually cooperation. If the company wants the patent, it will help defend it. If the company isn't interested, the inventor can find other licensees in the free market.

Now think about venture investors. Today, when a venture company dies, patents are often its best surviving assets. But separated from the engineers who did the work, the patents have only a fraction of their real worth. If the patents remain with the engineers, the asset would be not just a possible future cash flow. The asset would comprise the patents; all the other IP (intellectual property) associated with applying them, including collected data, prototypes, and so forth; and the actual people who did the work. This asset is a far more valuable—and tangible– one that a buyer could exploit at once.

Finally, there is an even more serious problem that the industry must address. Some investors now see patents as financial instruments: contracts that entitle the owner to an—admittedly uncertain—future cash flow. Investment banks can buy and pool patents and then create financial derivatives

based on these pools. Financial technicians can model those future cash flows as stochastic processes, applying the math used for collateralization of subprime mortgages. We

all know the next chapter in that story. The new demand for patents undermines the whole concept of IP in the United States.

So let inventors own their patents and allow them to transfer limited rights under the well-developed body of licensing law. It's fair to engineers. It's best for corporations and investors. And it could prevent a catastrophe that today threatens the entire system.EDN

Contact me at ronald.wilson@reed business.com.

# EDITED BY FRAN GRANVILLE

# **INNOVATIONS & INNOVATORS**

# Low-power audio codec incorporates Class D-loudspeaker amplifier

Ational Semiconductor recently announced the low-power LM49352 audio codec (compressor/decompressor) for handheld consumer electronics. The part includes an audio codec with ground-referenced headphone amplifiers, Class D-loudspeaker outputs, and an audio DSP. The loudspeaker delivers 93% efficiency at 970 mW from a 4.2V supply. The headphone amplifier offers 18-mW MP3 playback to extend battery life. Applications include smartphones, full-featured phones, portable gaming devices, and portable GPS (global-positioning-system) devices.

The device integrates a charge pump to increase power to the loudspeakers. It also includes a DAC, which achieves 103-dB SNR (signal-to-noise ratio), and an ADC, which provides 97-dB SNR. The part can play back audio with 96-kHz sampling rates and can record audio at 48 kHz. It also incorporates dualstereo, five-band parametric equalizers; ALC (average-level control); and limiter and com-

The low-power LM49352 audio codec for handheld consumer electronics has Class D-amplifier outputs.

pressor functions on both the DAC- and the ADC-signal paths. The codec also features differential-microphone inputs to minimize noise, crosstalk, and RF susceptibility. The ADC has a wind-noise filter that can operate in voice- or high-fidelity-recording modes.

The LM49352 comes in a 36-bump micro SMD package, sells for \$7.55 (1000), and is available for sampling, along with evaluation boards.—**by Paul Rako**

**National Semiconductor**, www.national. com.

# FEEDBACK LOOP

"Thanks ... from an old guy just doing FPGAs for the first time (after decades of microcontrollers). I'm sure you just saved me a week somewhere."

-Engineer and EDN reader Ernie Murphy, in EDN's Feedback Loop, at www.edn. com/article/CA6648806. Add your comments.

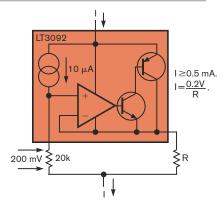

# Two-terminal current source supplies 200 mA

Linear Technology Corp's new LT3092 two-terminal current source can supply 0.5 to 200 mA of current at a 1% initial accuracy. The device operates at 1.5 to 40V and exhibits less-than-1-mV typical load regulation and less-than-0.001%/V typical line regulation. The device needs no bypass capacitance on the input or the output in most ranges of operation, even when you use it at 0.5V. The output is short-circuit-protected and can withstand reverse voltage, and a thermal-shutdown circuit prevents overheating. You can configure the devices in parallel for greater current, or you can stack them in series for greater voltage compliance.

The LT3092 comes in 3×3-mm, eight-pin DFN; eight-pin SOT-23; and three-pin SOT-223 packages. The LT3092MP version operates in the -55 to  $+125^{\circ}$ C junction-temperature range, and the LT3092E and LT3092I versions operate in the -40 to  $+125^{\circ}$ C range. Prices range from \$1.65 to \$4.73 (1000). For more on this product, go to www. edn.com/090611pa.**-by Paul Rako**

**Linear Technology Corp**, www.linear.com.

The two-terminal Linear Tech LT3092 current source works at 1.5 to 40V and can output 0.5 to 200 mA.

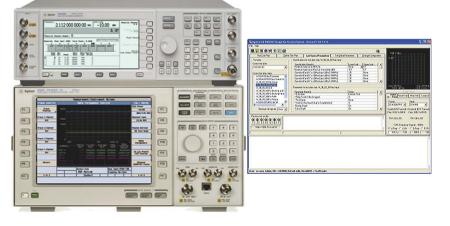

# Agilent, ETS-Lindgren address A-GPS test

gilent Technologies Inc has introduced GS-9000 A-GPS (assisted-global-positioning-system) test systems employing the company's 8960 wirelesscommunications-test set's new A-GPS-assistance-datamessaging-test capabilities. Meanwhile, ETS-Lindgren also announced an integrated test capability employing its AMS-8000 series of antenna-measurement systems and A-GPS test equipment from Agilent and other instrument vendors.

A-GPS, an enhanced position-location method, uses positioning-assistance data it obtains from base stations. With assistance data, a mobile device can within seconds determine and report back its exact location to a network. In contrast, unassisted-GPS techniques require minutes to accomplish this task. As service providers move to implement A-GPS in their networks and as vendors introduce A-GPS-capable devices, these devices require testing to demonstrate that A-GPS operation poses no interference to cellular services.

Agilent's GS-9000 A-GPS design-verification-test systems include both hardware and software for testing a device's A-GPS capabilities in a conducted environment. The hardware includes an 8960

# A-GPS uses positioningassistance data to determine and report back its exact location.

test set and an E4438C vector-signal generator to emulate GPS satellites. The GS-9000 enables A-GPS validation, TIS (total-isotropic-sensitivity) testing, and A-GPS preconformance testing for mobile devices; the system also provides fading and SUPL (secure-user-plane-location) support. A GS-9000 Lite version omits

Agilent's basic mobile-device A-GPS test setup includes the Agilent 8960 wireless-communications-test set, the E4438C ESG vector-signal generator, and PC-control software.

# **DILBERT By Scott Adams**

SUPL and fading capabilities.

Within the GS-9000, the 8960 test set acts as a base station with an A-GPS message pipe for sending A-GPSassistance-data messaging to and from the wireless device or phone under test. The phone acknowledges receipt of the data and performs location calculations, returning its location information to the 8960 test set through the appropriate UMTS (universal mobiletelecommunications system) or CDMA (code-division-multiple-access) 2000 technology-dependent protocol messaging. The system supports TIS testing in accordance with Version 3.0 of CTIA's (Cellular Telecommunications Industry Association's) "Test Plan for Mobile Station Over the Air Performance" by antennameasurement-system providers, such as ETS-Lindgren.

For its part, ETS-Lindgren announced an expansion of the company's AMS-8000 series of antenna-measurement systems, which include a fully anechoic RF-test chamber with DUT (device-undertest) positioning equipment, antennas, instrumentation, and test-automation software. Version 1.07 of its EMQuest EMQ-100 antenna-measurement software adds support for A-GPS and other RSS (received-signal-strength)-based measurement methods. The ETS-Lindgren system supports the Agilent A-GPS test equipment and Spirent Communications' (www.spirent.com) ULTS (UMTS-location-test system). -by Rick Nelson

► Agilent Technologies,

www.agilent.com.

► ETS-Lindgren, www.

ets-lindgren.com.

# pulse

# Kits support design of field-oriented-control motor drives

nfineon has expanded its range of application kits that support design of energyefficient motor drives employing the company's 8- and 16-bit microcontrollers. The focus of the kits is ease of use, according to Jürgen Hoika, senior product-marketing manager of the company's industrial- and multimarket-microcontroller group. The kits include comprehensive tools and scalable reference designs.

The company based the new kits on members of the 8bit XC800 and 16-bit XE166 families; they allow you to implement techniques such as FOC (field-oriented control) and power-factor control to obtain quiet and efficient designs. You need specific architectures to execute these techniques, Hoika says, but you can use an 8-bit device—when it has dedicated additional processing with a vector-computation block. A 16-bit control-

# These kits are not just reference designs but ready-to-use, complete applications.

ler, with a suitable architecture, runs two motors with both FOC and power-factor control.

Infineon based the dualmotor-drive kit on the XC878 and XE166, and it supports FOC and power-factor control with a scalable architecture from 8 to 16 bits and a power board driving as much as 8A at 110 to 230V. The FOC-motordrive kit supports design of FOC for the XC878 and XE166, with-in this case-a power board that drives as much as 7.5A at 23 to 56V. Code generation for the FOC aspect of your design is automatic. The 12V BLDC (brushless-dc)-

The dual-motor-drive-application kit supports FOC and powerfactor control with a scalable architecture from 8 to 16 bits and a power board driving as much as 8A at 110 to 230V.

drive kit uses the XC866 to drive motors with as much as 20A at 9 to 18V. All the kits contain a tool chain, including a compiler and a debugger; you can design with a library of preconfigured hardware and software blocks; a USB (Universal Serial Bus)-to-JTAG (Joint Test Action Group) and CAN (controller-area-network) bridge allows digital isolated real-time monitoring.

All of these kits work with Dave Drive, Infineon's autocode generator for motor drives. They are not just reference designs but ready-to-use, complete applications. For example, the dual-motor-drive kit contains two drive cards: One employs the XC878 with its vector computer, twin PWM (pulse-widthmodulation) units, and an ADC with 1.5-µsec sample time; the other employs the XE164, which hosts a MAC (multiply/ accumulate) unit, three PWM units, and two independent fast ADCs.

This device operates two motors and a PFC (power-factor-correction) block in parallel. The power board provides an inverter with 900 to 1800W, a second inverter with 100 to 200W, and a boost converter for power-factor control. In addition, you can run your application with control of induction motors for guick evaluation.

The 12V-BLDC kit with the XC866 costs €249 (approximately \$330), the FOC-motordrive-application kit sells for €399 (approximately \$530), and the dual-motor-driveapplication kit sells for €499 (approximately \$665).

−by Graham Prophet **Infineon**, www.infineon. com.

# STANDARDIZATION BOOSTS SOFTWARE REUSE IN MICRO-CONTROLLERS

ARM licensees build ARM's CMSIS (Cortexmicrocontroller-softwareinterface standard), a vendor-independent hardware-abstraction layer for processors, with Cortex-M processor IP (intellectual property). ARM intends to define a scalable interface standard across all Cortex-M series-processor vendors, enabling easier code sharing and reuse. Consistent and simple software interfaces to the processor-for silicon vendors and middleware providers-will lead to an easier learning curve for novice microcontroller developers and reduce product-development times.

In ARM's scenario, using 8- or 16-bit parts has no price benefit, and the automatic choice is the 32-bit single-chip microcontroller with ample memory, ensuring wellstructured software layers. Most microcontroller projects reuse software components-but only inhouse and only on a single device or device family. The CMSIS approach includes the creation of standard drivers for welldefined components that operate free of conflicts with middleware and operating systems from multiple vendors.

For more on this topic, go to www.edn.com/ 090611pb.

-by Graham Prophet ARM, www.arm.com.

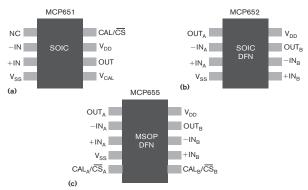

# Op amp has offset calibration to 200 $\mu$ V

icrochip Technology's new MCP651/2/5 operational amplifier targets use in microphone preamplifiers, optical-detector circuitry, digital scales, industrial instrumentation, H-bridge drivers, bar-code scanners, transmission-line drivers, and medical equipment for patientmonitoring and ultrasound functions.

The device has a maximum

supply voltage of 5.5V and a minimum supply voltage of 2.5V. Input-noise voltage density is  $7nV/\sqrt{Hz}$  with a flickernoise corner of 30 kHz. The device has a 50-MHz-gainbandwidth product and can output 95 mA of current. The op amp has rail-to-rail outputs and an input structure that allows input-common-mode voltages 300 mV below the negative-supply voltage. It requires 1.3V

The MCP65x offset-calibrating-op-amp series is available in single eight-pin (a), dual eight-pin (b), and dual 10-pin versions (c). of common-mode head room below the positive-supply voltage. The output-slew rate is  $30V/\mu$ sec, and the supply current is 6 mA. The typical input-bias current is 6 pA, and the maximum is 5000 pA at 125°C.

The device comes in a 10-pin DFN package with an extra pin for the calibration function.

When you pull the pin low, the part enters a calibration routine using an onboard DAC and memory and delay counters. The pin initiates an offsetvoltage correction within 200 msec. Another version comes in a standard eight-pin-package pinout without calibration pins, so it performs the correction only on power-on and within 4 msec.

The device has an operating-temperature range of -40

VOS Eval Board

board allows you to evaluate the capabilities of the MCP652 op amp.

to +125°C. Samples are available now, and the vendor is accepting volume orders. The single-amp MCP651, dual eight-pin MCP652, and dual 10-pin MCP655 cost \$1.21, \$1.49, and \$1.58 (10,000), respectively.—by Paul Rako **Microchip Technology**, www.microchip.com.

# BRIAN'S BRAIN

DNBLOG

# CES 2009: the price of falling prices

Given the multiyear time span that elapses between when a new microprocessor architecture is proposed and when the first products based on that architecture appear, I honestly doubt that Intel (www.intel. com) anticipated the economic crisis now gripping the globe. So, while I can't give the company credit for prescient forecasting, I'm still struck by the lucky timing of its Atom unveiling.

The netbook and net-top phenomenon represents the first time I can recall since the initial unveiling of the notebook PC when CPU horsepower has taken a substantive step backward in the face of some other more compelling factor. In the desktop-to-laptop transition, consumers consciously chose

to lessen their CPU demands in exchange for factors such as lower system weight and longer battery life. And in the modern notebook-to-netbook and desktop-to-net-top era, system price reductions are the fundamental motivation.

Intel and partner Microsoft (www.microsoft.com) are doing their damndest to keep the notebook- and netbook-PC segments distinct, in the hope of preserving the size and profitability of the notebook segment fed by Intel's higher-end CPU families. Take the Atom N270 CPU found in the MSI Wind U100 netbook that I tested in my

study, for example. Intel's own Web site advocates pairing that particular Atom processor flavor with the Mobile Intel 945GSE Express chip set with 82801GBM I/O controller hub (ICH7M). That corelogic chip set has an archaic integrated graphics core, and it also supports only up to 2 Gbytes of system memory. OEMs also report that Intel insists that they use the N270 only with systems containing 10-in.-diagonal maximum LCD sizes.

The ascendance of the CPU-deficient netbook and net-top symbolizes a substantial change in the rules of the game, thereby providing perhaps the first (and last?) tangible opportunity for vendors to redefine the fundamental parameters of the computer.

The netbook phenomenon has opened consumers' eyes to the reality that they've long been buying far more CPU muscle than most of them require. Therefore, I suspect that the era of robust sales of competitively isolated, highperformance Intel microprocessors is largely drawing to a close.—by Brian Dipert

www.edn.com/briansbrain.

For the full post, go to www. edn.com/090611pd.

# pulse

# Texas Instruments announces dual 14-bit, 250M-sample/sec ADC

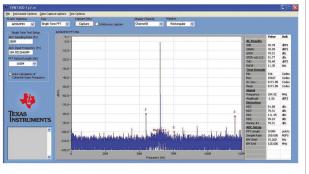

exas Instruments has introduced the dual 14-bit, 250M-sample/ sec ADS62P49 ADC, which achieves 73-dBFS (decibels relative to full-scale) SNR (signal-to-noise ratio) and 85-dBc (decibels referenced to the carrier) SFDR (spurious-free dynamic range) at an input frequency of 60 MHz. Chuck Sanna, product-marketing engineer for high-speed products at TI, calls the device the industry's fastest dual 14-bit ADC, adding that it targets communications applications, defense imaging systems, and wideband and portable testand-measurement equipment.

Power consumption is only 625 mW per channel, reducing thermal footprint and increasing system efficiency in highdensity, multiantenna-basestation receivers and softwaredefined radios. Programmable gain and other user-selectable settings maximize design flexibility. Internal gain adjustment of as much as 6 dB in 1-dB

At an input frequency of 185 MHz, the ADS62P49 achieves a 79-dBc SFDR, which extends to 91 dBc if you exclude the second- and third-order harmonics.

steps allows customers to optimize SNR, SFDR, and input swing based on their applications' needs. For instance, designers can maximize SNR to enhance linearization effectiveness in DPD (digital-predistortion) applications, or they can increase SFDR and reduce input drive to improve smallsignal analysis in defense and radio-receiver applications.

The device forms a part of a complete signal chain; complementary products include the DAC5682Z and DAC5688

DACs, the THS4509 amplifier, the TRF3703 and TRF3761 RF components, the GC5325 DPD-transmitter processors, the CDCE72010 clockdistribution circuit, and the TMS320C6727B DSP. A comprehensive evaluation-tool suite speeds time to market. Customers can leverage TI's TSW1200 digital-capture tool for rapid evaluation of LVDS (low-voltage-differential-signaling)-output ADCs with as much as 16-bit resolution and 500M-sample/sec rates to enable prototyping of complex systems and to further speed development time.

"Communications, defense, and test-design engineers are constantly challenged to create signal- and data-acquisition receivers with increasingly wide signal bandwidths," says Art George, senior vice president of TI's high-performanceanalog-business unit. "The ADS62P49 delivers highperformance [and] compact, power-efficient designs and enables rapid deployment of systems, software-defined radios, and spectrum analyzers."

The ADS62P49 is available in a  $9 \times 9$ -mm QFN package for \$144.75 (1000). The ADS62P49EVM evaluation module has onboard sockets for a voltage-controlled crystal oscillator, a crystal filter, and TI's newest high-performance clock-distribution and jitter-cleaning chip, the CDCE72010, which allows the module to function as a system-level evaluation kit and an ADC evaluation board.

−by Rick Nelson **Texas Instruments**, www. ti.com/ads62p49-pr.

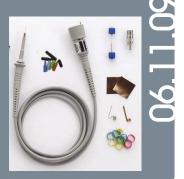

# PASSIVE SCOPE PROBES OFFER BANDWIDTHS TO 1.5 GHz FOR HIGH-SPEED-DIGITAL APPLICATIONS

Agilent Technologies has introduced the N2870A family of miniature passive oscilloscope probes and accessories with bandwidths from dc to 1.5 GHz. The probes' 2.5-mm-diameter heads cover only onefourth the surface area of earlier probes' 5-mm-diameter heads. The devices also offer low input capacitance and a variety of finepitch probe-tip accessories.

The probes and accessories allow you to probe densely populated IC components and surfacemount devices. The sharp, spring-loaded probe tip helps you keep the probe from slipping off the device under test. Insulating IC caps center the small probe tip on the IC lead and keep it from shorting to adjacent leads. Optional probe-tip accessories provide specialized capabilities for demanding applications.

The probes are available with attenuation ratios of 1-, 10-, 20-, and 100-to-1 and probe bandwidths of dc to 35, 200, 350, and 500 MHz and 1.5 GHz. The company's Infiniium 9000 series oscilloscopes come with one 500-MHz, 10-to-1-attenuation-ratio N2873A passive probe per channel. These probes have an input impedance whose resistive component is  $500\Omega$ . Prices for N2870A series probes begin at \$300.

-by Dan Strassberg Agilent Technologies, www.agilent.com/find/ N2870A.

The N2870A family of passive scope probes and accessories targets frequencies as high as 1.5 GHz. The 2.5mm-diameter head and the large number of accessories suit the probes for use on tiny components and crowded printed-circuit boards.

# **RESEARCH UPDATE** EDITED BY RON WILSON

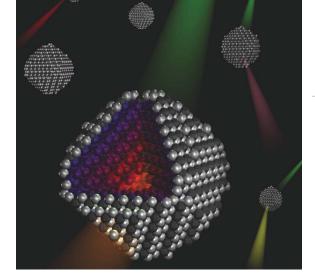

# New "nonblinking" nanocrystals promise increased efficiency in LED lighting

B LEDs (high-brightness light-emitting diodes) lose about 17% of their energy due to quantum losses, such as imperfections in the crystalline structure, or to a "blinking" effect. To address these problems, the University of Rochester with help from Kodak (www.kodak.com) and the US Naval Research Lab (www.nrl.navy.mil) has developed a nanocrystal that holds promise for eliminating losses due to blinking in LEDs, which show up as heat, a bugbear of solid-state-lighting designers.

"Many molecules, as well as crystals just a billionth of a meter in size, can absorb or radiate photons," says Todd Krauss, professor of chemistry at the University of Rochester and lead author on the study. "But they also experience random periods when they absorb a photon, but, instead of the photon radiating away, its energy is transformed into heat. These 'dark' periods alternate with periods when the molecule can radiate normally, leading to the appearance of [their] turning on and off, or blinking. A nanocrystal that has just absorbed the energy from a photon has two choices to rid itself of the excess energy: emission of light or [emission] of heat. If the nanocrystal emits that energy as heat, you've essentially lost that energy."

Krauss and fellow research-

This nonblinking nanocrystal holds promise for eliminating losses due to blinking in LEDs, which show up as heat (courtesy Ted Pawlicki, University of Rochester).

er Alexander Efros from the Naval Research Laboratory conclude that nanocrystals normally have a core of one semiconductor material wrapped in a protective shell of another, with a sharp boundary dividing the two (Reference 1). "The new nanocrystal, however, has a continuous gradient from a core of cadmium and selenium to a shell of zinc and selenium. That gradient squelches the processes that prevent photons from radiating, and the result is a stream of emitted photons as steady as the stream of absorbed photons," they state. Krauss

refers to the new nanocrystal as being a possible successor to cheap, printable OLEDs (organic LEDs), which are just beginning to find use in displays despite significant drawbacks, such as short lifetimes.—by Margery Conner DINVERSITY of Rochester, www.rochester.edu.

REFERENCE

■ Wang, Xiaoyong, Xiaofan Ren, Keith Kahen, Megan A Hahn, Manju Rajeswaran, Sara Maccagnano-Zacher, John Silcox, George E Cragg, Alexander L Efros, and Todd D Krauss, "Nonblinking semiconductor nanocrystals," *Nature* Magazine, May 10, 2009, www.nature.com/nature/ journal/vaop/ncurrent/full/ nature08072.html.

# IMEC DEVELOPS DESIGN FOR DEEP-BRAIN-STIMULATION IMPLANT

IMEC (Interuniversity Microelectronics Center) revealed a design strategy for brainstimulation implants at the recent DATE (Design, Automation, and Test in Europe) conference in Nice, France. IMEC researchers claim to have created a prototype multielectrode stimulation-and-recording probe for deep-brain stimulation, which could hold promise for medical treatment of Parkinson's disease. "To have a more precise stimulation and recording, we need electrodes that are as small as individual brain cells," says Wolfgang Eberle, senior scientist and project manager at IMEC's bioelectronics research group. "Such small electrodes can be made with semiconductor-process tech-

A deep-brain probe using microelectronics processes could stimulate and measure local areas in the brain, allowing more precise therapy.

nology, appropriate design tools, and advanced electronic-signal processing."

The IMEC group focuses on the brain-computer interface between biological and electronic systems. The group designs processes, components, and prototype microsystems for neuroelectronic interfaces that can bidirectionally exchange information with neurons through electrical mechanisms. The strategy allows for the development of advanced brain implants comprising multiple electrodes.

Multiphysics-modeling company Comsol supplied the finite-element modeling of the electrical-field distribution around the brain probe using multiphysics-simulation software. Comsol tools made it possible to investigate the mechanical and structural properties of the probe during surgical insertion and the effects of temperature. By adapting penetration depth and field asymmetry, steering the electricity around the probe results in precise stimulation. For an expanded write-up on this research, go to www.edn.com/090611pc.-by Gail Flower

Interuniversity Microelectronics Center, www.imec.be.

SIGNAL INTEGRITY

# BY HOWARD JOHNSON, PhD

# **Endpoint distortion**

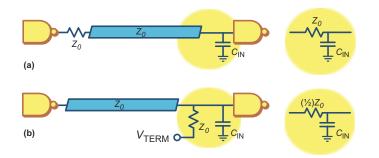

igure 1a and Figure 1b depict two common transmission-line scenarios: series termination and end termination, respectively. Both drivers are fast with negligible series output resistance. The capacitive loads represent the input capacitances of the CMOS receivers. In the series-terminated case, a step edge from the driver proceeds to the right, interacts with the load, and reflects back toward the driver. The capacitive load may cre-

ate a strange-looking reflection, and it may distort the appearance of the received signal, but whatever bounces off the load returns to the driver ter-

mination and dies, never to be seen again. As a result, the receiver sees one step edge, possibly distorted but with no lingering aftereffects. Of all the things that could go wrong with a circuit, this distortion is not too bad.

Figure 1 illustrates an equivalentendpoint circuit that defines the nature of instantaneous signal distortion at the receiver. The equivalent circuit comprises two components: a series resistance equal to the line impedance, and a shunt capacitance representing the input capacitance of the receiver (Reference 1).

The RC lowpass filter thus formed

disperses the input rise time. It also delays the signal's time of arrival by an amount equal to the group delay of the filter, in this case  $Z_0C_{IN}$ .

If your native signal rise or fall time is much faster than  $Z_0C_{IN}$ , then the filter slows the signal edge to the point where it mimics the filter step response-a nice, clean rising edge with a 10 to 63% rise time of  $Z_0C_{IN}$ . If, on the other hand, your native signal rise or fall time is slower than  $Z_0C_{IN}$ , the filter has little effect. If you look closely, however, you will see that the filter delays the time of arrival of the signal's midpoint by the amount  $Z_0C_{IN}$ .

In Figure 1b, a parallel combination of the transmission line and the

end termination feeds the capacitive load. If the end termination is properly set equal to  $Z_0$ , the parallel combination must be less than  $Z_0$ , so the load in this case responds more quickly, causing less distortion than in the series-terminated case.

If the PCB (printed-circuit-board) trace delay is longer than the signal's rise or fall time, the effective impedance at the end of the trace, which you measure on a scale of time commensurate with one rising or falling edge, equals simply  $Z_0$ . In that case, the parallel impedance driving the capacitor is  $(\frac{1}{2})Z_0$ , and the time constant associated with the RC filtering effect is  $(\frac{1}{2})Z_0C_{IN}$ , half that of the series-terminated case. On the other hand, if the PCB trace delay is shorter than the signal rise time, the effective impedance at the line's end decreases as it becomes a mixture of the driver and the line impedances, even further reducing the time constant.

The good news is that end terminations respond quickly. The bad news is that the capacitive load degrades the performance of the end termination. Upon receipt of each signal edge, the degraded termination reflects a short pulse back toward the driver. The driver has no termination, so it reflects the pulse a second time. The end of the line thus receives an initial distorted signal edge followed one round trip later by a small reflected pulse.

When signal timing fidelity is of utmost importance, the end-terminated architecture provides the least risetime dispersion and variation in timing in response to variable load capacitance. In exchange for its improved short-term response, the end termination suffers the possibility that roundtrip reflections will interfere with subsequent bits.EDN

# REFERENCE

Johnson, Howard, "Driving-point impedance," EDN, May 14, 2009, pg 12, www.edn.com/article/ CA6656309.

# TAPE-OUT COMES A LOT FASTER WITH CALIBRE NMDRC.

INTEGRATED SYSTEM DESIGN + DESIGN FOR MANUFACTURING + ELECTRONIC SYSTEM LEVEL DESIGN + FUNCTIONAL VERIFICATION

**Calibre® nmDRC** There's nothing like having an advantage when you're racing to market. That's exactly what you get with Calibre nmDRC. Widely recognized as the world's most popular physical verification solution, Calibre's hyperscaling architecture produces the fastest run times available. To accelerate things even more, Calibre nmDRC adds incremental verification and a dynamic results-viewing and debugging environment. Designers can check, fix and re-verify DRC violations in parallel, dramatically reducing total cycle time. Start out and stay ahead of the pack. Go to mentor.com/go/calibre\_nmdrc or call us at 800.547.3000.

# **USB 3.0:** A SIMPLE IDEA FULL OF CHALLENGES

COMBINING 5 GBPS WITH THE CONVENIENCE OF USB SOUNDS LIKE A SURE WIN, BUT MANY ISSUES ARE HIDING BEHIND THE PREMISE.

# BY RON WILSON • EXECUTIVE EDITOR

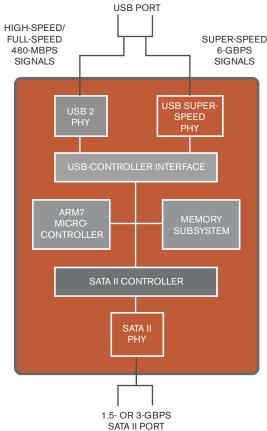

uper-speed USB (Universal Serial Bus) 3.0 sounds like a great idea. Just start with widely used, fast, and bulletproof USB 2.0 and graft in the PHY (physical-layer) interface from another common and reliable standard, PCIe (peripheral-component-interconnect express) Generation 2. Put two differential pairs into the USB connector to carry the high-speed serial signals from the Generation 2 PHY, and

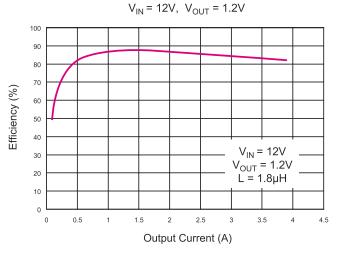

you have a rugged, flexible, inexpensive interface that can operate at 5 Mbps over consumer-priced cables and connectors with interfaces cheap enough to drop into a flash drive. The idea promises to unleash new ways of using PCs with mobile devices and with storage. With application-level throughput approaching 400 Mbytes/sec and the ability to simply plug anything from a flash drive to 3m of USB cable into a host, users could link PCs and netbooks, quickly dump the contents of huge flash drives, or easily transfer HD (high-definition) video between devices. They could even create their own external storage networks (**Figure 1**). This promise of speed and flexibility, however, carries the seeds of a difficult challenge for chip, board, and system designers.

"The concept of simply using a PCIe Gen 2 PHY in a USB controller is appealing," observes Mike Pennell, vice president of engineering at fabless-semiconductor supplier SMSC (Standard Microsystems Corp). "But you have to remember that, although the USB 3.0 PHY is based on the PCIe Gen 2 PHY, the media over which the two controllers must send data are very different. USB lives in a much more challenging world than [does] PCI."

Navraj Nandra, director of product marketing at Synopsys, explains further: "The similarity between PCIe Gen 2 and USB 3.0 stops at the speed," he says. "They both run at 5 Gbps. PCIe has to successfully work over only 20 inches of carefully designed PCB [printed-circuit board]."

Pennell says that the connection between a USB 3.0 host controller and a device controller could be far more complex than just using FR (fireretardant)-4 material. The connection would include several inches of PCB, a connector pair, a short pigtail running to the host's enclosure, another connector pair at the back of the enclosure, the 3m cable, another connector pair on the back of the target device, another pigtail, and another PCB. All together, those components make up a highly attenuating channel full of opportunities for strong reflections, and it is highly variable.

People don't often discuss the variability issue in USB, but it becomes hugely important at speeds of 5 Gbps, according to Nandra. "Even at USB 2.0, some certified USB cables are better than others," he warns. "Even wonderful, \$50 cables can degrade over time. We have already at the relatively low speeds of USB 2.0 seen poor cable performance impact the performance of the PHY. And, at 3.0, the problem will be much worse."

Cable experts agree that variability is an issue. Peter Smyth, chief executive officer of activecable vendor RedMere Technology, points out that you can make a USB 3.0 cable good enough to meet the specifications. Doing so also requires tight manufacturing

### AT A GLANCE

USB (Universal Serial Bus) 3.0 brings 5-Gbps speed to USB by blending USB with a PHY (physicallayer) interface it derives from PCIe (peripheral-component-interconnect express) Generation 2.

Combining USB with PCle Generation 2 presents significant design challenges.

System designers may have difficulty distinguishing a great PHY from a poor one.

controls, which cost a lot of money, however. And, even with the best controls and within a production run, cables can vary significantly. Then there is the problem of those pigtails, which no one seems to notice much. "That pigtail that runs from the PCB to the back of the

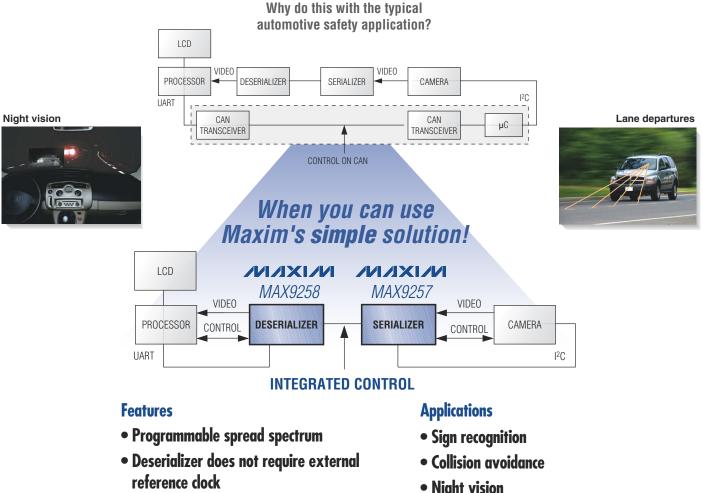

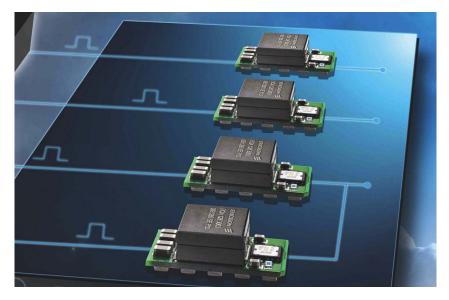

Figure 1 As USB 3.0 interfaces appear in mobile PCs, adapters such as this TI USB-to-SATA bridge will also show up.

box is typically just awful," says Smyth. System designers may find that they have used up most of their eye opening just getting to the back of their own boxes. And, because cables that consistently meet the 3.0 specification will be expensive to manufacture, the door will be open for counterfeit cables. So chip and system designers both must assume the worst—mediocre board design, poor pigtails, cheap connectors, counterfeit cable, and even a wire-bond package for the PHY—when planning their approaches to the new standard.

Unfortunately, successfully pumping 5 Gbps through a messy channel isn't the only problem. The channel is also highly variable. One minute, a port could have a thumb drive plugged into it, and, the next minute, someone could plug 10 feet of cable into a cage full of disk drives. So the PHY must be flexible. Just to make matters more interesting, USB 3.0 will

> start out expensive, but, by 2011, it will probably be standard in netbook computers and handheld consumer products, such as cameras, media players, and flash drives. The interface must have a migration path to becoming low cost, meaning that it will require an advanced process node. Andbecause a flash drive, to name one technology, draws its power from the USB cable itself-the interface must be low enough in power to allow cable-powered operation. The USB 3.0 standard will allow a device to draw as much as 900 mA during operation, but it must draw no more than 150 mA before configuration. That limitation itself demands a wellstudied power-management strategy at the chip level, which the system designer must understand in detail. All of these issues represent significant departures from the requirements that spawned PCIe 2.0.

### **CREATING A PHY**

Much of the responsibility for getting a data stream through the travails of a USB 3.0 channel will fall on the transmitter pre-emphasis circuit and, especially, the receiverequalization circuit. Interestingly,

the 3.0 specification appears to leave the design of these two blocks up to the chipdesign team. "One of the big differences between PCIe Gen 2 and USB 3.0 is that the PCI document specifies an eye-diagram template at the receiver input," says Synopsys' Nandra. "You have to get the signal there at a specified quality. But, in USB 3.0, the eyes can be so closed by the time the signal gets through the cable that there is no opening to put a template into. So, instead, the 3.0 document specifies an eye-diagram template at the output of the equalizer, not at the input to the receiver."

One of the greatest differences between PCIe Gen 2 PHYs and USB 3.0 PHYs will be in the receiver-equalization circuit. Many designers expect the quality of this block to be a major differentiator in the market, for PHY-IP (intellectual-property), chips, and the systems that use them. The equalizer must be both powerful in its action and adap-

# WHY DO WE NEED A 5-GBPS USB?

Why would most USB (Universal Serial Bus) users today even want so much speed in a USB link? After all, USB is supposed to provide flexibility and convenience for using mice, printers, flash drives, and the like. Consider flash drives, however. Capacity for the largest thumb drives has soared into the gigabytes, so transferring a significant portion of the contents of one of these drives through USB 2.0 can be a painful task. Meanwhile, marketers point to the supposed emergence of the home-media PC. with its enormous data files-think entire HD (high-definition) movies-and network-attached storage. Having a 5-Gbps version of USB would allow most home-media users to simply plug their external drives into their USB ports and not worry about the mysteries of SATA (serial-advanced-technology-attachment) or storage-area networks.

Also, forecasters expect a huge growth over the next few years in netbook computers and other mobile computing, Web-accessing, and media-gulping devices. Today, about the only option for creating a high-speed link between such a mobile device and your home PC is to set up a home network, complete with the hardware hassles and administration problems. A single USB cable would be a much simpler approach. And companies such as PLX Technology are working on protocols for using SuperSpeed USB as a virtual network between computers.

Jimmy Chou, director of marketing for storage and USB products at PLX Technology, forecasts that consumer PCs will be the early adopters of USB 3.0, with discrete PHY (physical-layer) chips going into notebooks early next year. A lot of notebook vendors have such designs under way now, he suggests. Meanwhile, other sources suggest that makers of handheld devices that trade in large data files, such as videocameras and movie players, may be on a similar time line.

A big milestone will arrive when Intel, in about 18 months, releases a south-bridge chip with integrated 3.0. With that announcement, momentum should grow until 3.0 has become universal by mid-2011, according to forecasts. Predictably, the fly in the ointment may be software. Chou says that the host-side driver for 3.0 is about an order of magnitude more complex than the device-side driver. Device vendors will also have to supply some code to the host to execute with the resident host driver. Microsoft does not plan to release any host driver for 3.0 before the Windows 7 servicepack 1, according to industry talk. So, it may turn out that, for all the added hardware complexity that USB 3.0 is imposing on chip vendors, the real delay may be in just getting the drivers right.

tive. Otherwise, a PHY would be unable to handle the range of channel conditions that USB can throw at it. As an adaptive equalizer, this circuit will require a training sequence to lock onto. Yet, the equalizer must be low in power and compact to meet the needs of consumer-product applications. Those challenges are formidable.

Also, although PCIe Gen 2 is a fully synchronous interface, Nandra points out, USB 3.0 requires that the PHY use a spread-spectrum clock in a way that makes the transmitter and receiver essentially asynchronous. The receiver CDR (clock- and data-recovery) circuit must recover the transmitting clock without having access to the spreadspectrum signal that modulated it. "That requires a very elastic CDR," observes SMSC's Pennell.

Such issues will make previous expe-

# THE FIRST STEP IS TO RUN ALL THE CIRCUITS AS SLOWLY AS POSSIBLE TO CON-SERVE ENERGY.

rience with PCIe Gen 2 a real asset for chip designers. "If a design team has really understood PCIe Gen 2, then they can adapt about 90% of their work to USB 3.0," says Scott Kim, manager of business development at Texas Instruments. Yes, the equalizer will need beefing up, but much of the circuitry will remain the same. For example, getting 5-Gbps performance from the PHY requires a careful trade-off between deep pipelining to meet throughput requirements and limited latency to meet bus timing.

Kim also emphasizes the importance of experience with power management. "The first step is to run all the circuits as slowly as possible to conserve energy," Kim says. "For instance, you have to keep the receiver listening for the LFPS (low-frequency-periodic-signaling) traffic so that you know when to wake up. But that [requirement] doesn't mean you have to run the whole receiver at full speed. We've figured out a way to filter LFPS while running at very low power." Kim also cites TI's extensive low-powerdesign method, which now routinely includes clock gating and power gating. Such techniques allow designers to run the transmitter-pre-emphasis circuit at varying power levels, depending on the needs of the channel. Similarly, Synopsys 3.0 IP will reduce receiver-equalizer power to just the level the circuit needs for the required equalization.

All of these challenges represent a substantial investment, in both design and testing, according to Jimmy Chou, director of marketing for storage and USB products at PLX Technology. PLX has the benefit of an established presence in both USB 2.0 and PCIe Gen 2, but Chou says that the engineering investment was still substantial. In addition to the usual costs of chip design, he says, the company has spent about a year and a half in the lab testing and validating its PHYs, especially the equalizer algorithms.

### LEGACY TROUBLES

One of the serious implementation challenges with USB 3.0 turns out to be the requirement that the PHY operate simultaneously in both legacy USB 2.0 mode and 3.0 mode. Most design teams have looked at the problem and concluded that the best approach is to simply drop a commodity USB 2.0 PHY-IP block into the design next to the newly designed 3.0 hardware. TI, for example, takes this approach, and most IP vendors will probably also do so. The cell exists in their libraries, so why not just use it? According to Synopsys' Nandra, however, there are good reasons not to. At the layout level, you can combine the digital portions of the two PHYs and save some real estate. With cleverness, you can also reduce the pin count of the block and the frontage on the perimeter of the die. More important, according to Nandra, is the fact that a lot of signals must pass between the 2.0 and 3.0 PHY devices during operation. It may be unwise to expose these internal signals to the chip designers who don't know the details of USB 3.0 operation.

Nandra also worries about crosstalk when both 2.0 and 3.0 modes are in simultaneous operation. He points out that, if you are using a continuous-time + Go to www.edn.com/090611df and click on Feedback Loop to post a comment on this article.

+ For more technical articles, ao to www.edn.com/features.

linear equalizer, turning up the gain on the equalizer won't help because doing so amplifies not just the signal, but also the crosstalk. So you may have to implement active crosstalk-suppression circuitry for simultaneous operation.

With complex channels varying in characteristics, power and cost constraints, legacy compatibility issues, and some lingering questions about the robustness of the standard, USB 3.0 is not a walk in the park. Given the range of applications (see sidebar "Why do we need a 5-Gbps USB?") and the momentum behind the standard, however, IP and chip vendors will support the effort. They will present system designers with a variety of choices with different price and power points.

It may prove exceedingly complex for system vendors to determine exactly what kind of performance they are getting for their dollar and their milliwatt, however. Extensive testing with board layouts, different lengths and qualities of cabling, and varying connector quality may be the only way to tell the really top-quality PHY, which can deliver consistently high data rates and low biterror rates, from the bargain-basement PHY, which will work well only under ideal conditions.EDN

# FOR MORE INFORMATION

Intel Corp www.intel.com Microsoft www.microsoft.com PLX Technology www.plxtech.com RedMere Technology www.redmere.com

You can reach Executive Editor at 1-510-744-1263 and reedbusiness.com

Standard Microsystems Corp www.smsc.com Synopsys www.synopsys.com **Texas Instruments** www.ti.com

Over 2500 Std. **DC-DC Converters**  Surface Mount •From 2V to 10,000 VDC Output •1-300 Watt Modules Isolated/Regulated/ **Programmable Models** Available •Military Upgrades Available Custom Models, Consult Factory See full Catalog immediately

www.picoelectronics.com

Engineering Assistance Call Factory or send direct for FREE PICO Catalog Call toll free 800-431-1064 in NY call 914-738-1400 Fax 914-738-8225

**Electronics, Inc.** 143 Sparks Ave. Pelham, N.Y. 10803-18889 **INDUSTRIAL • COTS • MILITARY**

**RF ENGINEERS** OMATE TESTS

BY MARTIN ROWE • SENIOR TECHNICAL EDITOR, TEST & MEASUREMENT WORLD

esting of RF devices, such as amplifiers and RFICs (radio-frequency integrated circuits), can be tedious work. Such devices work over a wide range of frequencies and power levels, and they must meet specifications over temperature and powersupply ranges. Testing for all of those conditions can generate loads of data. Fortunately, automation can cut test time and help you make sense of all that information. You may have a spectrum

analyzer, a network analyzer, or a power meter with features that can improve testing, but you may be unable to use the instrument if you must maintain compatibility with older models. If you're testing leading-edge RF products, your test equipment may lack the necessary dedicated features, and you'll have to develop your own.

MANY TEST ENGI-

TIES IN TODAY'S RF-

**OWN ALGORITHMS,**

AUTOMATED TESTS.

Bill Drago, a test engineer at L-3 Communications' Narda Microwave East (www.nardamicrowave.com/east), supports production of RF amplifiers, downconverters, upconverters, and transceivers that operate in the C through Ka bands. These products often remain in production for years, which is the reason that Drago is unable to take advantage of features in newer test equipment that can automate many of the measurements he needs to make. He developed his tests before such automation was available, and he needs all of his test instruments to continue to follow identical procedures. Thus, he has written software that performs automated measurements, such as amplifier gain, 1-dB compression, IMD (intermodulation distortion), return loss, spurious noise, and noise figure. Accord-

ing to Drago, spurious-noise testing is important. "Downconverters and upconverters mix an input signal with a local oscillator," he says. "The converter's local oscillator must be tuned to customer specifications within a certain range and step size. The converter needs a frequency synthesizer that's programmable with specified steps over its frequency range. The frequency synthesizer can't introduce any spurs into the converter, so we must test for that."

To measure spurious noise, Drago uses an Agilent Technologies (www.agilent. com) spectrum analyzer to perform a frequency sweep through an approximately 1-GHz band around the carrier. He usually breaks that sweep into a number of smaller sweeps, each comprising 601 frequency points. Each step might be a few kilohertz wide. If Drago were to use one large sweep, its step size and the instrument's resolution bandwidth would be too wide and might miss a spur. He adjusts sweep span and resolution bandwidth so that spurs don't fall between the points in a sweep. Using a number of smaller sweeps is also faster than a single sweep for the bandwidth that Drago needs. He notes that a single sweep could take as long as an hour, depending on resolution bandwidth and frequency. Furthermore, smaller sweeps can reveal failures sooner than waiting for a large sweep to complete.

Although some of Drago's spectrum

analyzers have built-in test applications for measuring spurious noise, he doesn't use them, because not all of his spectrum analyzers have that function. If he were to use that feature, he might not have a replacement instrument for the production line should that instrument fail. Instead, he wrote his own applications, and, by keeping the test applications outside the instrument, he can use any spectrum analyzer that's available.

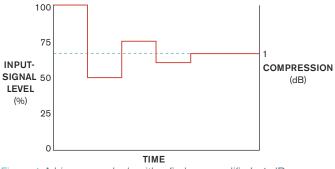

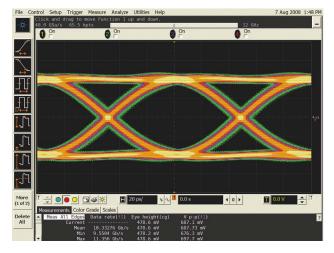

Drago has written several other test programs, including one that measures an amplifier's 1-dB compression point. He

builds this test into some of his VNAs (vector-network analyzers). The algorithm uses a binary-search process, similar to the type that SAR (successive-approximationregister) ADCs use. He starts with an input signal from an Agilent RF-signal generator that's the highest possible value for the amplifier under test. He then measures output power with an Agilent RF-power meter. If the output signal is com-

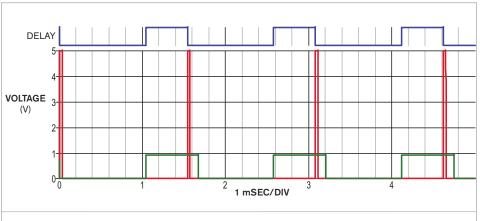

pressed by more than 1 dB, he cuts the input signal in half and then increases it or decreases it by half of that value until he finds the 1-dB compression point (Figure 1).

# **FINDING HARMONICS**

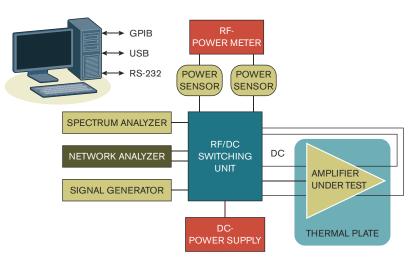

Michael Ford is a test engineer at Comtech PST (www.comtechpst.com), a manufacturer of RF amplifiers that operate at 500 MHz to 6 GHz at power levels of 100W to 10 kW. Ford's typical test station contains an RF-signal generator, a spectrum analyzer, a network analyzer, a power meter, and RF switches (**Figure 2**). A USB (Universal Serial Bus) digital-I/O module from Measurement Computing (www.measurementcomputing.

### AT A GLANCE

Testing over temperature and power-supply ranges can generate lots of information, and automation can help you make sense of it.

Engineers may or may not use an instrument's built-in functions, depending on the needs of both their customers and the design teams within their companies.

GPIB (general-purpose-interface-bus) communications are good for sending a series of short commands, whereas Ethernet works with the logic analyzer to collect data on digital-baseband signals.

With loop-back testing, a manufacturer can wirelessly test a Bluetooth product as it moves along a production line.

com) controls the RF switches. The amplifiers mount on an environmental plate that changes their temperature. The test station measures gain, output

Figure 1 A binary-search algorithm finds an amplifier's 1-dB compression point (courtesy L-3 Communications).

power, harmonic distortion, IMD, efficiency, spurious noise, and harmonics.

On occasion, Ford uses an instrument's built-in functions. For example, he might measure spurious noise with an Agilent spectrum analyzer's built-in application. But he also writes his own applications to make those measurements if his instrument doesn't have that feature. Ford supports both engineering and production. When making measurements for engineering evaluations, he uses built-in functions, such as spurious noise and harmonic analysis. For production, Ford always uses his own software routines. "We write our own routines using a modular format because it lets us use equipment from multiple vendors, such

as Agilent or Rohde & Schwarz [www. rohde-schwarz.com]. We use the same test routines and just change instrument-command libraries." For example, his routine for spurious-noise measurements works with spectrum analyzers from either manufacturer.

Ford's routines for measuring harmonics of a carrier frequency use variables for parameters such as center frequency, span, resolution bandwidth, and video bandwidth. After receiving those parameters, the routine runs sweeps at multiples of the carrier frequency to find the power of its harmonics. The results go to a spreadsheet for analysis.

# **CELLULAR NETWORKS**

Although Drago and Ford must support products that remain in production for years, engineers developing tests for RFICs face different problems and have different reasons for not always using an instrument's automation features. Joe Flynn is a staff engineer at fablesssemiconductor company Sequoia Com-

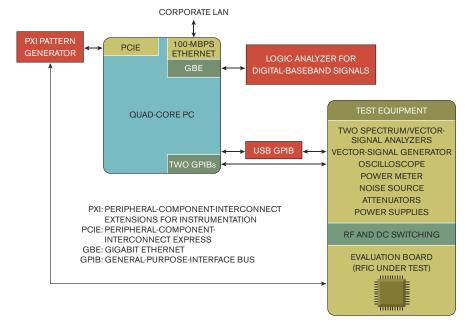

> munications (www.sequoia communications.com). He evaluates RFICs that support several cellular-wireless standards (**Reference 1**). He has developed several test stations for evaluating the devices. "We characterize transceivers for gain, noise figure, IMD, cross-modulation, and EVM [error-vector magnitude]," he says. Flynn also develops his own automation tools, but measurement speed is the critical

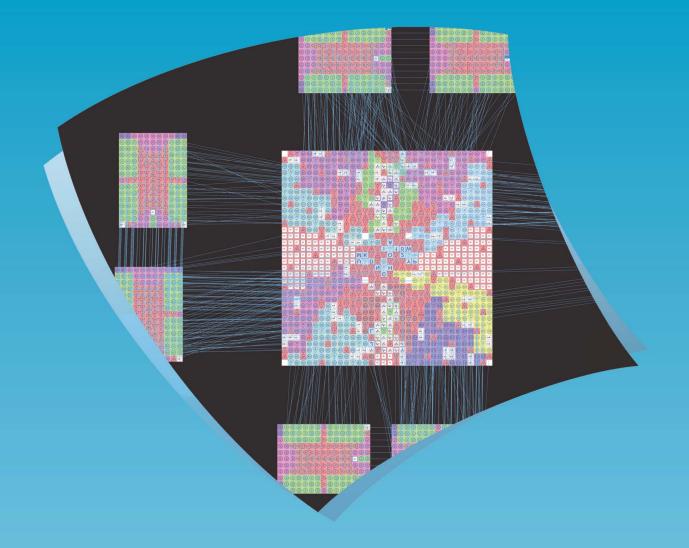

feature in choosing equipment. Because RFICs transmit and receive modulated signals, Flynn's test stations include spectrum analyzers for characterizing frequency content, and they include modulation analyzers for characterizing modulated content. Figure 3 shows a system that tests the receivers in Sequoia's ICs. The receiver test bench lets Flynn evaluate how a receiver performs in the presence of undesired blocking signals, such as those from simulated cellular base stations, other cell phones, and broadcast-radio stations.

As part of the blocking-signal test, Flynn must measure SNR (signal-tonoise ratio) over a frequency range of 100 kHz to 12.7 GHz in 200-kHz steps. That

task takes approximately 60,000 measurements per channel, and the RFIC has 1300 channels over seven frequency bands. An SNR test generates loads of measurement data, and it's just one of many tests that Flynn must run on a preproduction lot of parts. To help analyze the data, Flynn developed a data converter that produces data plots. The tool lets him use production-test-analysis tools to view engineering data. For example, he might want to see the distribution of parameters, such as gain, return loss, and current consumption across the 100 parts in a preproduction run. "When we look at the data, we get a feel for how production parts will behave," he says.

Sequoia also developed an in-house Visual Basic Web-based tool that manipulates the bench-characterization data. The tool uses .netCharting (www. dotnetcharting.com) software to create some 1200 data plots on the parts. "When we have a test review, the tool lets us find any out-of-spec measurements," he says. The tool lets him select data parameters to plot and refine the data by selecting certain test conditions. For example, it lets him look at receiver gain and noise figure versus temperature or power-supply voltage.

Because he must make so many mea-

Figure 2 A typical automated tester for RF amplifiers uses a power meter, a spectrum analyzer, a network analyzer, and a signal generator (courtesy Comtech PST).

surements, speed is key for Flynn when he selects a spectrum analyzer and develops a test method. To cut measurement time, he uses two Agilent MXA spectrum analyzers, one each for a receiver's in-phase and quadrature channels. The instruments are frequency- and phaselocked, which synchronizes the measurements. He then optimizes resolution bandwidth and sweep time to minimize test time: "When I started, a single SNR measurement on one channel at one

Figure 3 An RFIC-test station for testing receivers uses two GPIB cards and a LAN to communicate with instruments (courtesy Sequoia Communications).

blocker frequency took about a second. Now, I make each measurement in 18 msec." Flynn also learned how to minimize test time by using both LAN (local-area-network) and GPIB (generalpurpose-interface-bus) communications. Most instruments in the test system use GPIB because, according to Flynn, "You can't beat GPIB when sending a series of short commands. The overhead needed to use Ethernet is apparent only when transferring large blocks of data." Thus, he uses Ethernet for the logic analyzer, which collects data on digital-baseband signals. He also uses a dedicated GbE (gigabit-Ethernet)-LAN card to avoid packet collisions between the test equipment and the corporate network. He uses three GPIB cards to cover all of the test equipment.

### **MIX AND MATCH**

CSR (www.csr.com) is a fabless-semiconductor company that develops wireless-communication RFICs for PANs (personal-area networks), such as Bluetooth and Wi-Fi. James Blackwell, who heads the company's applications-engineering group, helps customers evaluate CSR's RFICs and develop products based on the company's devices. CSR engineers use a mixture of in-house and purchased test equipment, usually starting with in-house testers. "Because we're often on the leading edge," says Blackwell, "we have to develop our own test suites until the test-equipment companies catch up." One example is a Bluetooth tester for performing loop-back tests. Blackwell notes that the Bluetooth specification defines a loop-back test in which the tester wirelessly controls the DUT (device under test). With loop-back testing, a manufacturer can wirelessly test a Bluetooth product as it moves along a production line.

When CSR's engineers several years ago developed a Bluetooth RFIC, engineers had to build their own RF-test system using RF-signal generators, spectrum analyzers, and vector-signal analyzers. They used The MathWorks' (www. mathworks.com) Matlab scripts to control the instruments, process the data, and produce test reports. In a loop-back test, the tester commands the DUT to produce a 2.405-GHz tone with a specified modulation signal, for example. The tester measures as many as 20 parameters, such as peak and average transmitted RF power. It also performs receiver tests, such as sensitivity and bit-error rate.

Some Bluetooth devices transmit at controlled power levels, so the DUT must operate in steps in its power table while the tester measures differences in power. It also measures frequency tolerance and drift. A test of the frequency response of the DUT's modulation filter uses 10101010 and 11110000 bit patterns. Over time, test-equipment makers developed Bluetooth testers, and CSR was able to use them. Today, the company's engineers use Bluetooth testers from Rohde & Schwarz, Agilent, and Anritsu (www.anritsu.com). CSR has all three instruments, so the engineers always have one that their customers use. That requirement is crucial when an engineer needs to reproduce a customer's test.

CSR engineers didn't immediately switch to a dedicated Bluetooth tester. "We work with the test-equipment manufacturers to develop test applications for their equipment," Blackwell explains. "But sometimes we must wait for a second or third generation of a tester before we can use it. Even after we adopt a commercially available tester, we may still use our own test suites for certain tests." Blackwell notes that

VICOF

dedicated Bluetooth testers may perform some tests faster or more accurately than CSR's in-house testers, but the company's engineers still use the inhouse tester when they feel that it performs the tests better than a dedicated tester can.

# **TEST COMPANIES RESPOND**